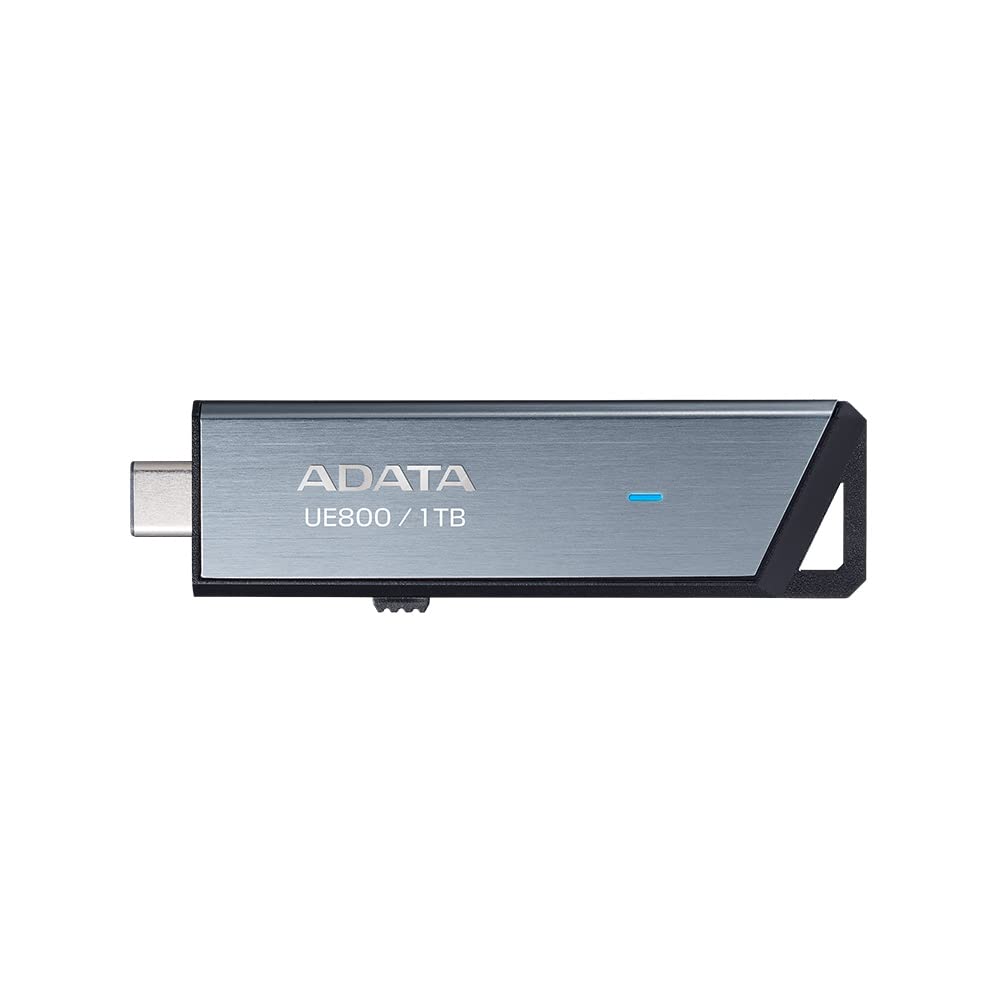

Pamięć flash to nieulotna pamięć półprzewodnikowa, którą można wielokrotnie zapisywać i kasować. Odczyt/zapis wykonuje się blokowo lub bajtowo. Typowa trwałość to 100000 cykli kasowania. Programowanie odbywa się przez zmianę ładunku elektrycznego w tranzystorze z izolowaną bramką. Pamięć flash znajduje zastosowanie w pendrive’ach, dyskach SSD, kartach SD i pamięciach BIOS. Kasowanie następuje przez przyłożenie dobrego napięcia do bramki tranzystora.

Pamięć Flash stanowi obecnie fundamentalną technologię przechowywania danych w elektronice. Mechanizm działania tej pamięci opiera się na zjawisku tunelowym w strukturach półprzewodnikowych, gdzie elektrony są przechwytywane w obszarze floating gate. Proces zapisu danych polega na wprowadzeniu ładunku elektrycznego do pływającej bramki poprzez przyłożenie wysokiego napięcia programującego. W nowoczesnych układach pamięci Flash stosuje się zaawansowane techniki wielopoziomowego programowania (MLC – Multi-Level Cell), pozwalające na zapisanie więcej niż jednego bitu w pojedynczej komórce. Technologia ta ewoluowała od prostych struktur SLC (Single-Level Cell) do bardziej złożonych implementacji, np. TLC (Triple-Level Cell) czy QLC (Quad-Level Cell).

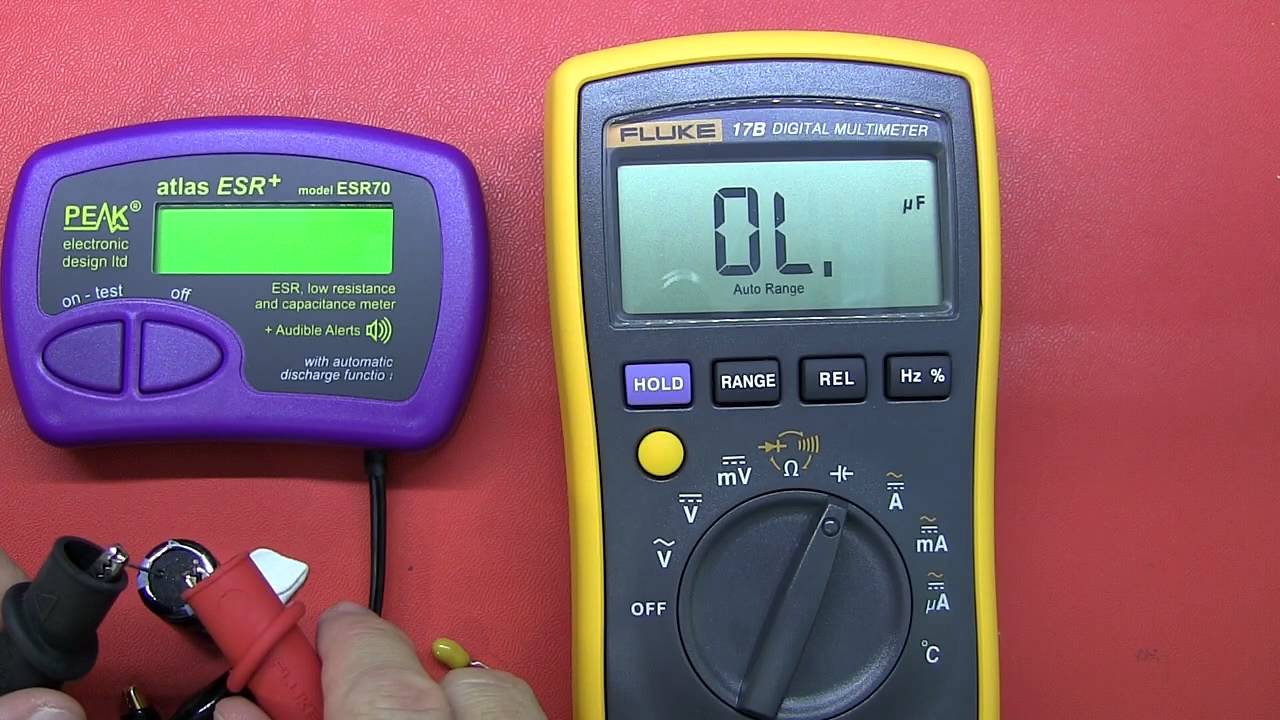

Operacja odczytu w pamięci Flash wykorzystuje zjawisko różnicy napięć progowych – zależnie ilości zgromadzonego ładunku w pływającej bramce. Jak dobrze zoptymalizować proces odczytu? To podstawowe pytanie dla projektantów układów pamięci. Aktualnie układy wykorzystują różnorodne techniki korekcji błędów (ECC) i zarządzania bad-blockami. „Wydajność odczytu determinuje szybkość dostępu do danych, co jest krytyczne w aplikacjach wymagających wysokiej przepustowości.”

Zaawansowane techniki programowania komórek pamięci

- Programowanie przyrostowe (incremental step pulse programming)

- Weryfikacja napięcia progowego po każdym impulsie

- Techniki kompensacji zakłóceń międzykomórkowych

- Dynamiczna regulacja parametrów programowania

Implementacja efektywnych algorytmów programowania wymaga uwzględnienia następujących spraw: Ważne znaczenie ma precyzja kontroli napięcia programującego oraz czasu trwania impulsów. Zjawisko degradacji komórek (tzw. wear leveling) wymusza stosowanie zaawansowanych technik równoważenia zużycia. Mechanizmy wear-levelingu (równoważenia zużycia komórek) są potrzebne do zapewnienia długiej żywotności pamięci.

Optymalizacja procesu odczytu i zapisu

Aktualnie kontrolery pamięci Flash implementują złożone algorytmy optymalizacyjne. Wykorzystują one buforowanie, predykcję dostępu oraz inteligentne mechanizmy garbage collection. Architektury wielokanałowe umożliwiają równoległy dostęp do wielu bloków pamięci (co mocno zwiększa przepustowość). Efektywność tych rozwiązań zależy od sposobu organizacji danych i implementacji niskopoziomowego oprogramowania sterującego. „Podstawą wysokiej wydajności jest zrównoważenie pomiędzy szybkością dostępu a niezawodnością zapisu.”

Tajniki pamięci flash w elektronice – co jest za za EEPROM?

Pamięć flash stanowi ważny element faktycznych urządzeń elektronicznych, wykorzystując technologię tranzystorów z pływającą bramką. Proces zapisu danych polega na wprowadzaniu ładunków elektrycznych do izolowanej bramki, co pozwala na długotrwałe przechowywanie informacji nawet po odłączeniu zasilania. Standardowy czas dostępu do pamięci flash wynosi od 70 do 100 nanosekund.

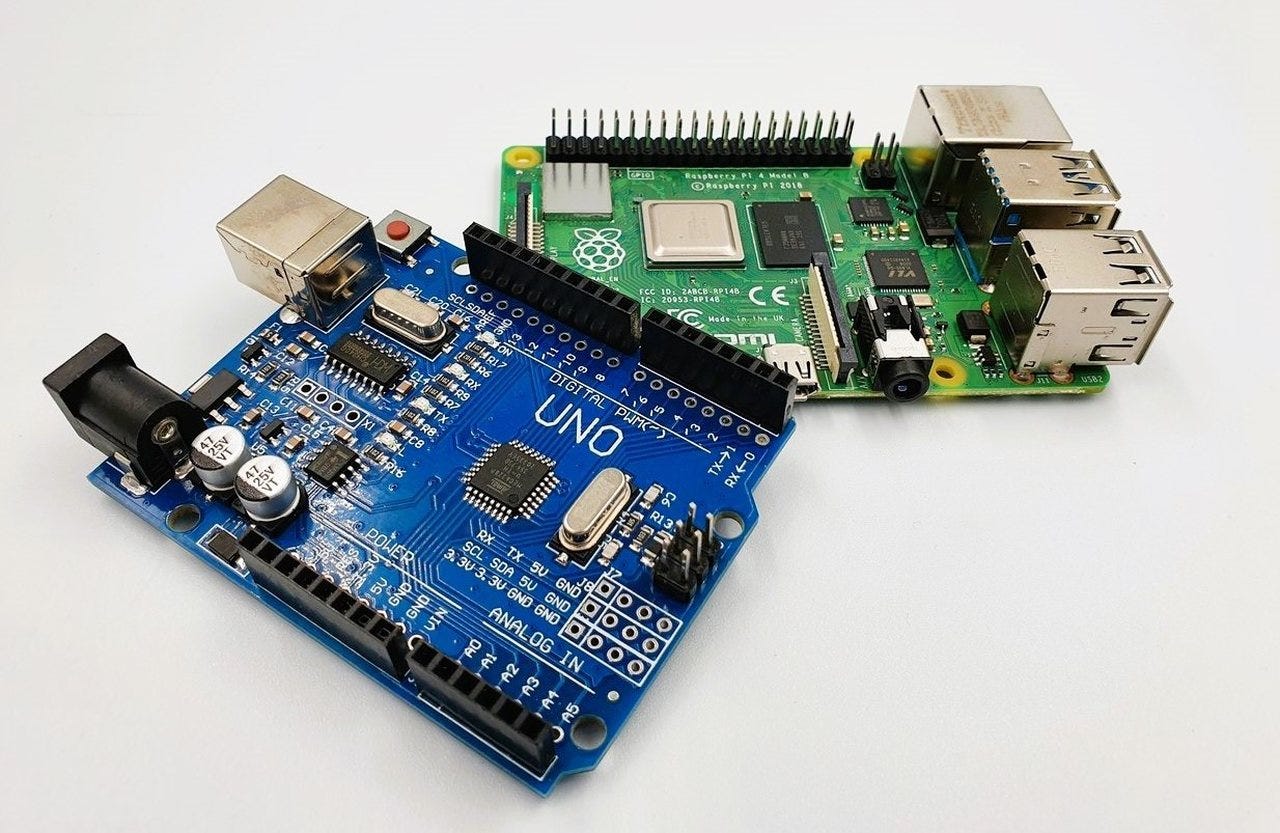

Najbardziej ciekawe interfejsy komunikacyjne to SPI oraz I2C, które umożliwiają prostą integrację z mikroprocesorami. Żywotność pamięci flash określa się zazwyczaj na poziomie 100 000 cykli zapisu-odczytu, co w większości celów wystarcza na wiele lat bezproblemowej pracy.

Producenci systematycznie zwiększają gęstość upakowania komórek pamięci, daje to coraz większe pojemności przy zachowaniu niewielkich rozmiarów fizycznych układu. Technologia MLC (Multi-Level Cell) pozwala przechowywać więcej niż jeden bit informacji w pojedynczej komórce, mocno zwiększając efektywność wykorzystania przestrzeni. Nowoczesne układy dają także zaawansowane mechanizmy korekcji błędów i wyrównywania zużycia.

Tajniki programowania pamięci flash przez SPI – podstawa do efektywnej komunikacji

Programowanie pamięci flash przez interfejs SPI stanowi fundamentalną metodę zapisywania danych w nowoczesnych układach elektronicznych. Protokół SPI (Serial Peripheral Interface) umożliwia synchroniczną, szeregową komunikację między mikrokontrolerem a pamięcią flash, wykorzystując cztery podstawowe linie sygnałowe: MOSI, MISO, SCK i CS.

- Inicjalizacja połączenia SPI

- Wysłanie komendy zapisu (Write Enable)

- Weryfikacja statusu pamięci

- Transmisja danych do zaprogramowania

- Potwierdzenie poprawności zapisu

Proces programowania rozpoczyna się od aktywacji układu poprzez linię CS (Chip Select), następnie wysyłane są odpowiednie komendy inicjujące operację zapisu. Zasadnicze jest przestrzeganie czasów programowania poszczególnych stron pamięci oraz weryfikacja statusu operacji.

Optymalizacja programowania pamięci flash w systemach o ograniczonej mocy

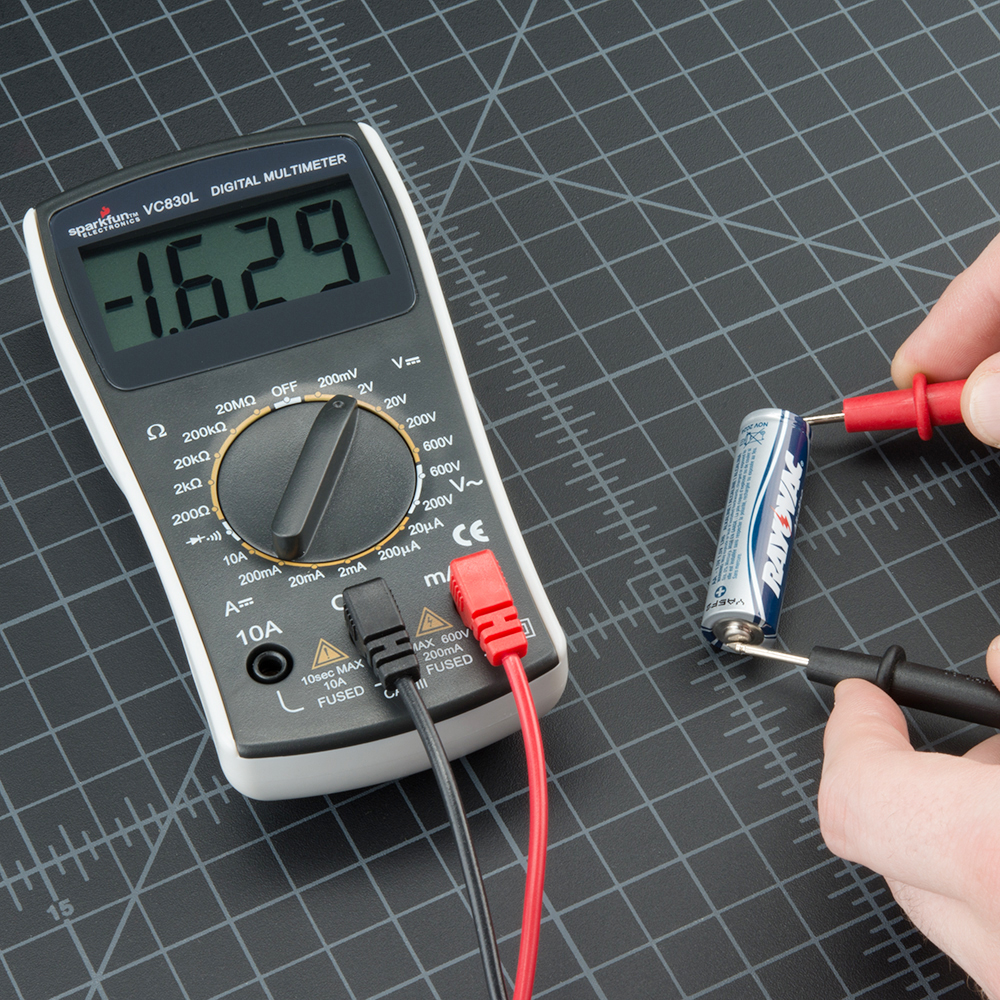

Dla systemów zasilanych bateryjnie, podstawowe znaczenie ma implementacja mechanizmów oszczędzania energii podczas operacji programowania. Wykorzystanie trybów uśpienia między operacjami zapisu oraz optymalizacja wielkości pakietów danych może mocno wydłużyć czas pracy urządzenia. Istotną rolę odgrywa także dobór dobrego algorytmu buforowania danych, który minimalizuje liczbę operacji zapisu do pamięci flash.

Wear leveling – Jak układy eeprom dbają o długowieczność pamięci?

Mechanizm wear leveling został stworzony, aby przedłużyć żywotność pamięci EEPROM poprzez równomierne rozłożenie operacji zapisu na wszystkie komórki pamięci. Każda komórka w układzie EEPROM ma ograniczoną liczbę cykli zapisu, najczęściej od 100 000 do 1 000 000 operacji, po których może ulec uszkodzeniu. Kontroler pamięci śledzi wykorzystanie poszczególnych bloków i dynamicznie zarządza miejscem zapisu danych.

System wear leveling wykorzystuje specjalne algorytmy mapowania, które przekierowują operacje zapisu do mniej zużytych obszarów pamięci. Za pomocą tego unika się nadmiernego obciążenia tych samych komórek.

Technologia ta jest szczególnie ważna w systemach przemysłowych i motoryzacyjnych, gdzie niezawodność jest elementarna. Stosowanie wear levelingu mocno wydłuża rzeczywisty czas eksploatacji urządzeń, pozwalając na miliony operacji zapisu bez ryzyka utraty danych. Nowsze implementacje tego mechanizmu potrafią a jeszcze optymalizować procesy zapisu pod kątem energooszczędności.